基于PCIe总线的多通道采集回放系统可实现高速信号的采集、存储及快速回放功能,坤驰科技的系统具备PCIe总线的快速数据传输能力、ADQ14、CSE126G1系列板卡的高速高精度数据采集能力、AWG2500系列任意波形发生器的快速数据回放能力,可实现单通道、12bit、6GS/s采样率采集;同时、可4通道、输入增益可调、14bit、1GS/s采样率采集;高速采集的同时可实现2通道、14bit、2.5GS/s 的任意波形回放。

系统组成如下图:

系统详细介绍:

系统硬件包括用户自选的PCIe总线的工控机箱;一款型号为ADQ14DC-4C-VG的4通道、14bit、1GS/s,可变输入增益、2GB内存的PCIe高速数据采集卡;一款型号为CSE126G1的1通道、12bit、6GS/s、4GB内存的PCIe高速数据采集卡;一款型号为AWG2500-64M的2通道、14bit、2.5GS/s、64Msamples板上内存的任意波形发生器。

系统模块介绍:

1)、ADQ14DC-4C-VG

规格:4通道,1GS/s,14bit,DC耦合

接口形式:PCIe

输入范围:(VG):0.5, 1, 2, 5 Vpp

连接器:SMA

-3dB带宽:700MHz

时钟:内/外时钟参考

触发:软件、内部触发、外触发输入/输出、电平触发

其他:双槽、支持GPIO、过压保护

FPGA:Xilinx Kintex 7 K325T、支持用户二次开发

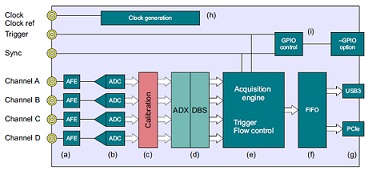

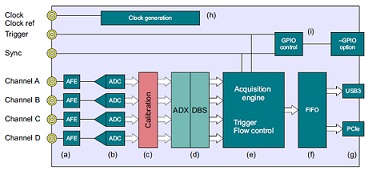

A)、板卡架构图

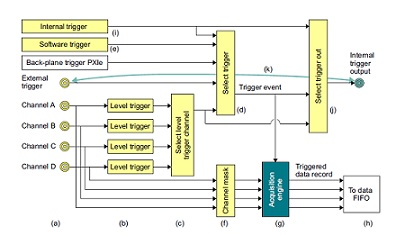

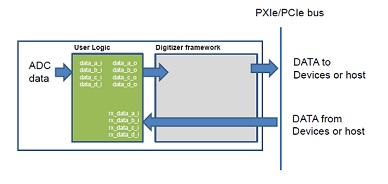

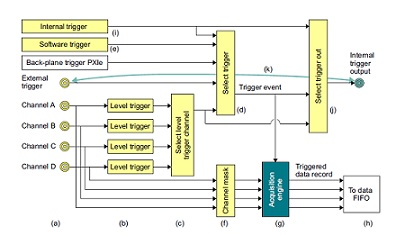

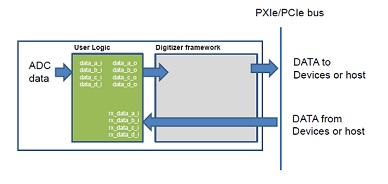

B)、数据流控制

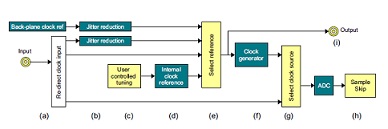

C)、时钟控制

D)、触发设置

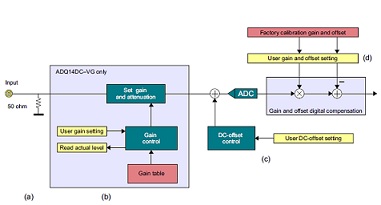

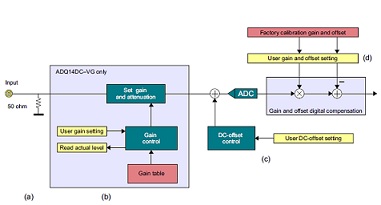

E)、模拟前端AFE设置

F)、触发模式

数据流模式(triggered streaming)-适合大化的利用数据传输到主机的速度

多段记录模式(multi record mode)-适合大量数据的实时采集

G)、采集控制设置

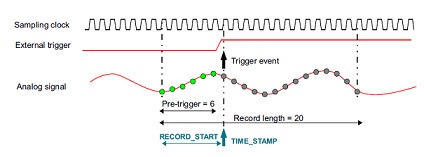

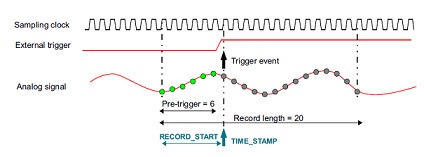

·Pre-trigger模式

注:数据流模式(streaming mode)下,预触发的长度是有限的,对比之下,多段记录模式下(multi-record)高可达234个采样点。

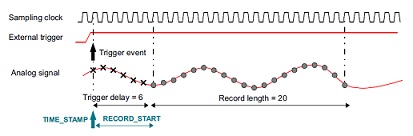

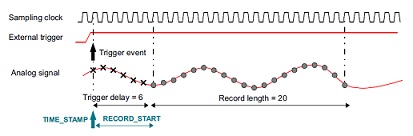

·Hold-off (Delay)模式

•延迟长度高可达234个采样点(取决于板卡模式)

H)、用户FPGA二次开发选项

SDK提供一些开发平台的编程实例和参考工程,ADQAPI 参考指导详细的描述了所有功能,很多例子和应用笔记会有助于用户开发。使用SDK可帮助用户实现

数字化仪的大量数据处理和实时控制。

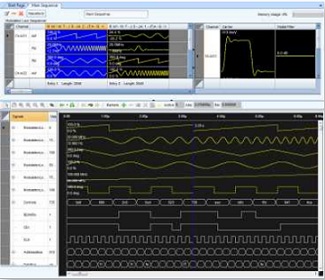

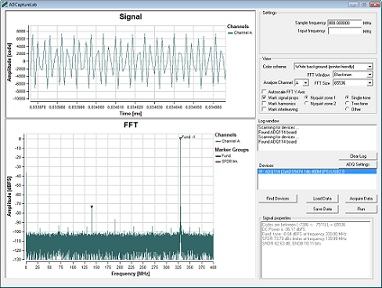

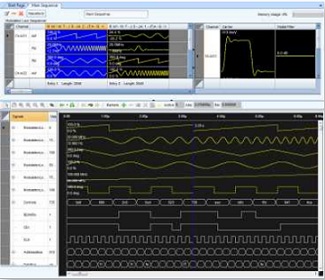

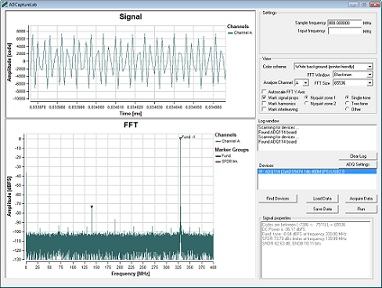

J)、板卡软件界面

•UI界面:ADCapture Lab

•C/Matlab/Python 采集例程可用

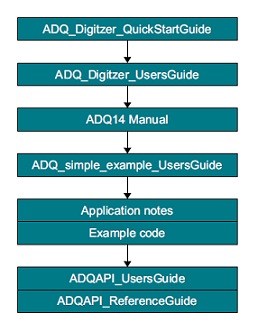

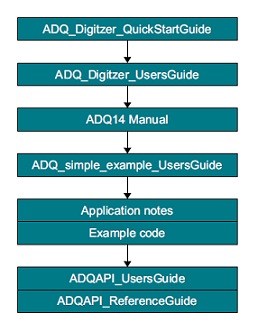

•ADCapture Lab安装后,安装目录生成以下丰富参考文件及API.

2)、CSE126G1

规格:1通道,6GS/s,12bit,DC耦合

接口形式:PCIe

输入阻抗:50?

输入范围:±100 mV, ±200 mV, ±500 mV,

±1 V, ±2 V, ±5 V(软件选择)

输入调节:直流偏置(输入范围内)

过压保护:±6 V

连接器:SMA

-3dB带宽:1.75GHz

板上内存:4GB

时钟:内/外时钟参考

触发:外触发输入/输出、电平触发

同步:可设置为多通道同步主/从模式

大传输率:4GB/s

FPGA:SDK开发包支持C/C#, LabVIEW ,MATLAB

操作界面:GaGeScope PC 示波软件

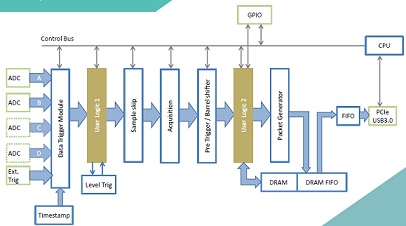

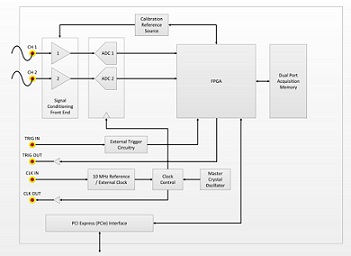

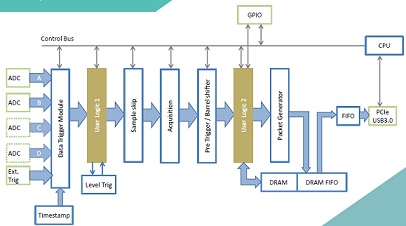

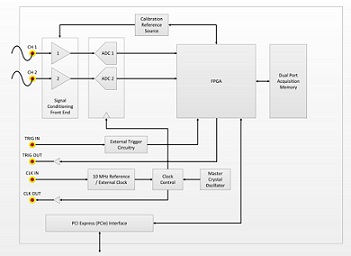

A)、板卡框图:

B)、触发

触发源:通道触发、外部触发、软件触发

组合触发:所有触发方式以“或(OR)”逻辑组合使用

触发信号要求:上升沿或下降沿(软件选择)

灵敏度:满量程触发源输入范围的±5%

C)、外部触发

连接器:SMA

匹配阻抗:1K ?

耦合方式:AC

带宽:>100MHz

电压范围:0-3V(非极性)

D)、触发输出

连接器:SMA

匹配阻抗:50 ?

幅度:0-TTL

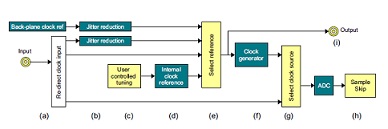

E)、时钟输入

连接器:SMA

电压:小0.2V RMS,大0.5RMS

匹配阻抗:50 ?

耦合方式:DC

占空比:50% ±5%

输入模式:外部时钟或10MHz时钟参考

F)、时钟输出

连接器:SMA

电压:0-1.5V

匹配阻抗:50 ?

占空比:50%

输出模式:半采样时钟频率或10MHz时钟参考

采样时钟:小 200MHz

模式速率:大3GHz

10MHz参考:10MHz(来自于外部时钟)

G)、多段模式

预触发长度:大为FPGA内存大小

H)、多卡系统

主/从(Master/Slave)模式:多通道系统的所有板卡的所有通道

独立模式:系统内每个板卡独立操作

J)、PC系统需求

PCIe插槽:1个全长PCIe gen1,gen2或gen3,x8或x16插槽

操作系统:Windows 7(32-bit/64-bit)

Windows 8 (32-bit/64-bit)

Linux – Requires SDK for C/C#

K)、其他指标

尺寸:单槽,全高、3/4 长

电源功耗:25W

3)、AWG2500-64M 任意波形发生器

规格:2通道,2.5GS/s,14bit

-3dB带宽:1GHz

DAC直接输出-DC耦合:1.6 Vpp 差分/ 0.8 Vpp 单端.

RF放大输出-AC耦合:-10 dBm to +10 dBm 差分输出

板上内存:64M/每通道

谐波失真:<-65 dBc

非谐波失真:<-74dBc (1kHz to 1GHz)

多通道同步:10ps分辨率控制

数字模式发生器:16/32 Bits @ 1250/625 Mbps

其他:任意、DDS和功能发生模式,先进的波形序列发生器

A)、特点:

RF信号发生功能

数字化模块设计

非常低的谐波失真

输出选择:RF放大,直接DAC输出、

DC放大

高速数字化输出

多个设备同步

任意、DDS和功能发生模式

B)、用户操作软件

功能易用操作软件

先进的任意(Arbitrary)/DDS 操作界面

带有环路,条件跳变和子序列功能的强大序列发生器