热搜关键词: PCIe高速数据采集卡RFSOC高速数据采集软件无线电平台VPX高速数据采集卡高速信号采集卡PCIe数据采集数字信号处理

✕

1,工作原理

|

|

描述

|

设置函数

|

|

a

|

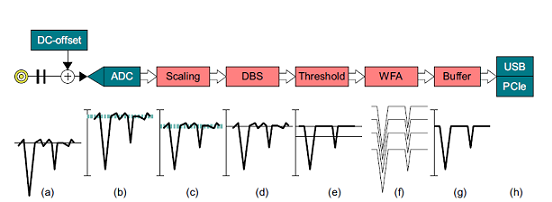

模拟信号为单极脉冲(负极)

|

|

|

b

|

将模拟的直流偏置(DC-offset

0加到信号,以充分利用ADC幅度

|

SetAdjustableBias

|

|

c

|

增益和偏移的数字化扫描

|

SetGainandOffset

|

|

d

|

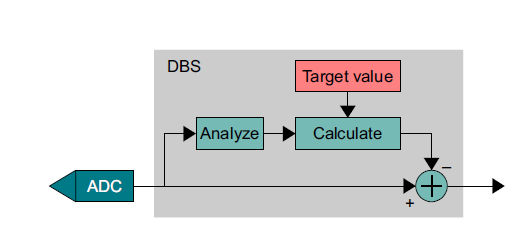

基线稳定器,DBS,脉冲数据系统内利用专有算法的基线稳定器,DBS输出是一个相对于用户定义值的约束控制等值线

|

SetupDBS

|

|

e

|

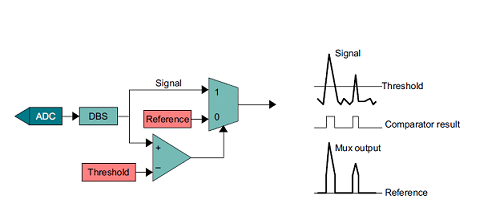

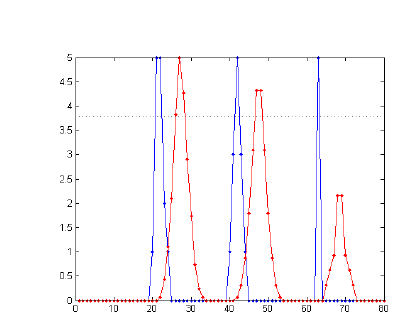

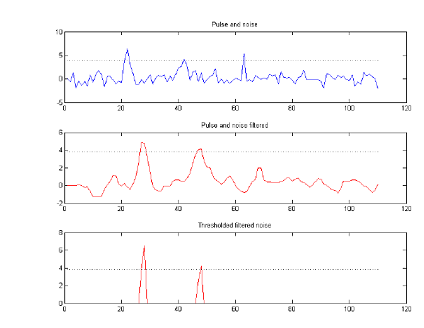

阈值运算操作为将噪声设置低于定义阈值以下的噪声压制,本处有一个用于信号加强的FIR线性滤波器和非线性噪声抑制的阈值电压

|

ATDSetupThreshold

ATDSetupFilter

|

|

f

|

用于噪声抑制波形平均重复测量一定数量的波形,

|

ATDSetupWFA

|

|

g

|

数据传输到主机,双buffer时,即使进行大量波形平均计算,空载时间(dead-time)不受限制。

|

|

|

h

|

数据通过 USB 3.0或PCIe 传到主机

|

See ADQ14 manual

|

2,模拟输入

3,零电位调准和信号缩放

4,数字基线稳定器,DBS

图2

5,高级阈值设置

5.1 概述

5.2 利用滤波器的线性噪声抑制

5.3 应用阈值

5.4 准确度

6.1 累加数据字

6.2 累加矢量长度

6.3 触发

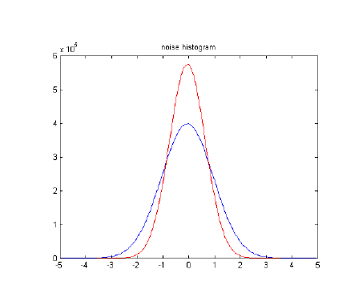

图7 滤波前后的噪声直方图